上一次我们讲到

计算机是一个会读会写的印度女工

要理解印度女工到底是如何进行读 / 写 / 跳转的,说来话长。它按照层次高低涉及以下方面:

- CPU 的微架构

- 核心的整体架构,包括寄存器、ALU、分支

- 内存层次。包括 Cache、TLB、内存(包括 DRAM 等)

- 其他的周边设备

- 数电内容:组合电路、时序电路(触发器、时钟)

- 模电内容:三极管

楼主考完模电就忘完了;另一方面,对 CPU 核心以外的讨论计划在今后的杂谈中进行。因此,本文主要顺着 数字电路 - 简单的核心元件 - 核心架构 这条脉络展开。

先来谈谈数字电路吧。

抽象一点说,数字电路就是在处理二值逻辑。可以被粗略地分为组合逻辑和时序逻辑两种。

组合逻辑 #

在电路中,高电平代表真,低电平代表假。只含有逻辑门的电路称为组合电路。它就像是二值信号的纯函数,输出仅和输入有关。

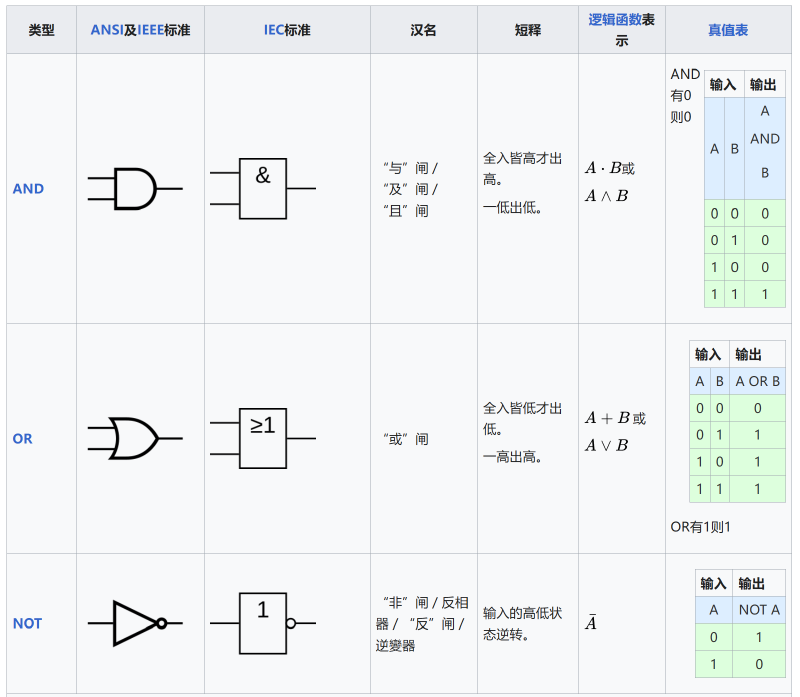

最简单易懂的三种逻辑门是与门、或门、非门。它们分别代表逻辑与、或、非。太懒了,直接从维基截个图好了

逻辑门之间可以相互组合,形成各种奇妙的功能。理论上,只要是一种“逻辑上静态的纯函数”,就可以被组合电路实现。举几个例子:

- 加法器:输入为 2 个固定位宽的数(例如同时有 4 条线,就是一个 4-bit 数,可以表示 0 到 15;两组这样的输入信号线,就可以作为两个 4-bit 数),输出为 1 个固定位宽的数(例如 4-bit),为两数之和。

- 选择器:输入为 X1(n-bit)、X2(n-bit)、choice(1-bit)。当 choice=0 时输出 X1,choice=1 时输出 X2。更复杂的选择器可以让 choice 为 n-bit,这样就允许有 $X_1, X_2, …, X_{2^n}$ 作为选项。

实际上,对于一整块组合电路,它的输入信号改变后,需要一小段时间才能看到输出信号的改变,这段时间被称为组合延迟。为了避免与时序电路中的概念混淆,以及为了便于科普,我们可以暂时认为接下来的讨论中组合延迟都为 0,输入信号的改变瞬间引起输出信号的改变。

时序逻辑 #

逻辑门、触发器、时钟构成的时序电路会一拍一拍地改变状态。

时钟 #

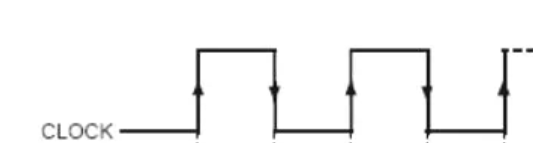

所谓的时钟就是按照固定频率交替输出高电平 - 低电平的元件。

在高低电平交替的那一刻,称为上升沿(低变高)和下降沿(高变低)。

触发器 #

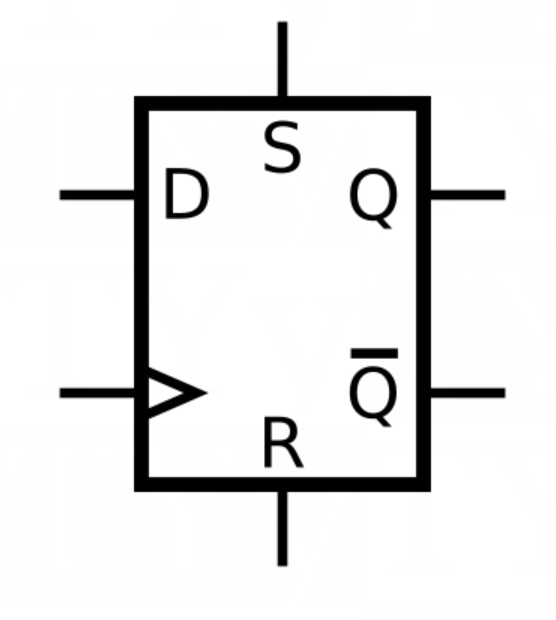

为了简便,只介绍 D 触发器。

为了讨论简单,忽略图中的 S、R、Q-hat。

三角符号接入上文提到的时钟。D 触发器就是一个“小格子”,它可以存储一个比特。这个比特在任何时候都直接反映在 Q 上。当时钟上升沿到来时,这一瞬间 D 的值会被存储下来。

我们可以想象这样一个图景:在一个电路板上有许多 D 触发器,它们全部接到同一个时钟上,并且一部分触发器的 Q 经过若干组合电路运算后,接到另一部分触发器的 D 上。这样,随着时钟一拍一拍地进行,所有 D 触发器都 同步 地改变自己存储的值。

是不是有点熟悉了?这就是实现“分支与跳转”的基本原理。

- 其实印度女工心里的所有数字都是用触发器存储的(称为 reg)。

- (在简化讨论中)她每次读到的指令也是触发器的数据(称为 inst)。

- 另外有一组触发器表示“程序执行到哪里了”(称为 pc)。

然后事情就简单了:所有这一切触发器都是按照时钟的节律同步变化的。当时钟上升沿到来时,印度女工更新 reg,同时也更新 pc(依据正是 inst、reg、pc 这三个经过一大坨 组合逻辑 后算出的结果)。

我们将在后面详细说明这一点。