为什么存储器需要层次结构 #

既然内存与寄存器在核心中的访问方式如此相像,为何要做两个部件?换句话说,为什么不将 register file 的寄存器数量从 32 个扩展到无限多个?这涉及到一个关键的 tradeoff:访问速度与容量。

我们在 CPU 核心中提到的有关内存的概念事实上被刻意简化了。在真实的计算机中,访问速度与容量是不可兼得的;这是因为更快的存储器是以更高的功耗、更复杂的电路为代价的;换句话说,在总功率、芯片总面积一定的情况下,能够支持的快速存储器的总额是有限的。

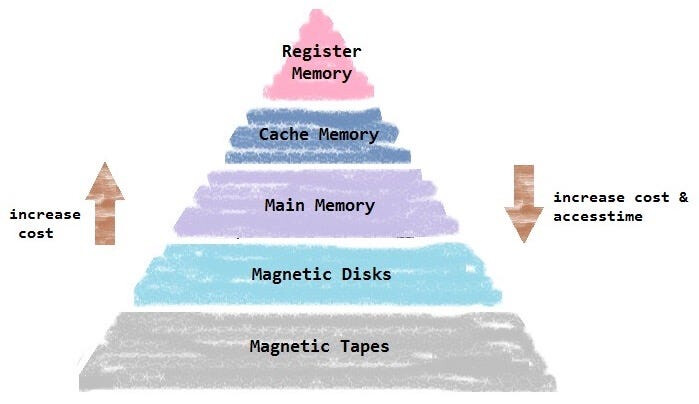

因此,计算机采取了一种直观且有效的解决方案:越快的存储器,它的容量就设计得越小,且放置得离 CPU 越近。计算机运行时,最远、最慢、最大的存储器拥有最完整的信息;最近、最快、最小的存储器只保存临时用到的部分数据,并随时按需要从低级存储器中提取和替换数据。

最快的存储元件:SRAM #

在前文中提过的寄存器,实际上指的是 SRAM(static random-access memory)。SRAM 通常使用 6 个晶体管保存 1 位数据。之所以叫“静态”,是因为和 DRAM 相对,不需要定期刷新,因此访问时间与 CPU 的周期时间十分相近,这与我们对 CPU 的简化描述中“组合读取,单周期写入”的抽象十分吻合。

SRAM 往往被用来实现寄存器和片上缓存。它虽然快,但是容量被设计得很小:L3 缓存通常最大为 12 MB,而与它配套的、用 DRAM 实现的主存储器容量可以达到 16 GB。与之对应的是,在缓存中最慢、最大的 L3 缓存,它的速度也是主存储器的 4~6 倍。

消逝的光芒:DRAM #

DRAM 容量更大,速度稍慢,被用来实现主存储器(即前文中提到的内存)。

为了在有限的空间内容纳更多信息,另一种方案是仅使用 1 个晶体管来存储 1 bit 信息。这样做的代价是:

- 读取该信息时,会破坏该信息,因此必须在读取后重新写入,因此读取不再是纯组合逻辑;

- 只使用一个晶体管来存储一位,这是不太稳定。为了防止在长期不读取的情况下丢失某一位,需要定期刷新存储器中的所有位,这意味着存储器对 CPU 而言会不定时地存在不可用时间。

- 复杂的 DRAM 控制器导致读和写都不再是单周期的,而是要遵循特定的协议与握手信号。这是因为存储器及其控制器的电路更复杂,组合延迟更高,因此它需要采用独立于 CPU core 的、更慢的时钟;这使得核心与主存之间的数据传输是异步逻辑。

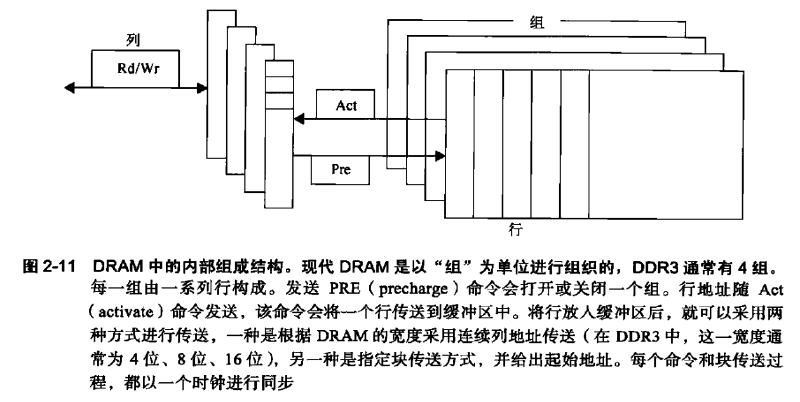

DRAM(dynamic random-access memory)名字的来源正是这种定期刷新的特性。DRAM 也存在自己的缓存:在处理器需要提取某个字时,包含这个字的整个行被发送到缓存,然后从该行中提取特定的字发往处理器,与此同时整个行被 DRAM 控制器刷新——这是一种十分精巧的设计,因为它把传送字与刷新的过程 重叠(overlap)了。

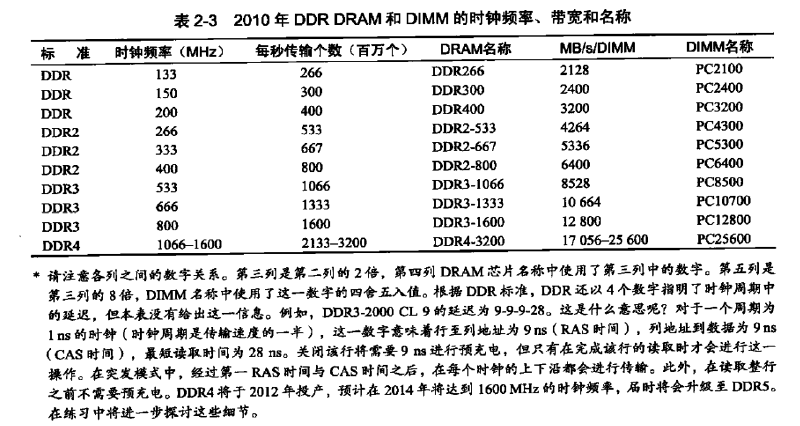

DRAM 原本与其控制器存在一个异步接口,这使得每一个传输都有一定开销;后来,人们给 DRAM 添加了一个时钟信号,这就是同步 DRAM(SDRAM)。注意这里的 S 是 sync 的意思,而不是 static。进一步,人们发现可以允许存储器在上升沿和下降沿都传输数据,这样传输速率就成了原来的 2 倍,这就是我们熟悉的 DDR(double data rate)SDRAM。

有趣的是,硬件厂商总喜欢大数字,因此 DDR 后面跟的数字并非它的频率,而是每秒字节数(这往往是频率的 2 倍),但在图吧我们经常能听到“3200 频率的 DDR4”这样的发言。

闪存 #

闪存是一种 EEPROM(电可擦可编程只读存储器),最常用的是 NAND 闪存,它们被用来实现 PC 的固态硬盘(你一定听说过闪存颗粒吧)和智能手机的存储器(UFS)。既然是只读,为何可以用来做硬盘呢?这是因为它是可擦除的。需要修改?控制器把整块都擦掉重写就好了。

闪存是一种 Non-volatile random-access memory(NVRAM),“非易失性”意味着它们断电后仍然保存数据,可以担任持久化存储的任务。

UFS(Universal Flash Storage)和 SSD 都以闪存为基础,区别是 SSD 的控制器更复杂、功耗更高、速度更快。因此 UFS 被用来作为智能手机的持久化存储,它们拥有更低的功耗,但代价是速度不如 SSD。

智能手机早期都支持插入外部的存储卡,这使得相对于存储卡而言,闪存是“内部存储”,因此经常能在手机参数中看到“256 GB 内存”这样的描述;这在讨论 PC 时是骇人听闻的,因为 PC 中的内外是相对 CPU 而言的,主存储器相对于硬盘离 CPU 更近,被称为内存,大小往往只有 8~32 GB,且是断电即丢失的。